FeRAMの特徴と原理、基本動作について

FeRAMは不揮発性メモリでありながら、揮発性メモリの長所を兼ね備えたメモリです。電源がオフでもデータが消えない不揮発性のほか、高書換え耐性や高速書込みの特徴も有しています。ここではFeRAMの特徴と原理及び基本動作について解説します。

FeRAMの特徴

FeRAM(Ferroelectric Random Access Memory)は不揮発性メモリでありながら、揮発性メモリの長所を兼ね備えたメモリです。不揮発性メモリの長所として挙げられる、電源がオフでもデータが消えない(不揮発性)・低消費電力の特徴に加えて、揮発性メモリの長所として挙げられる、データの書き換え保証の回数が多い(高書換え耐性)・高速書込みの特徴も有しており、これら4つを特徴としたメモリです。FeRAMと他のメモリ製品の特性比較を表1に示します。FeRAMは記憶素子に強誘電体材料を用いており、そのプロセス技術開発により、100兆回の高書換え回数や125℃高温対応を実現しています。

表1. メモリの特性比較

FeRAMの原理

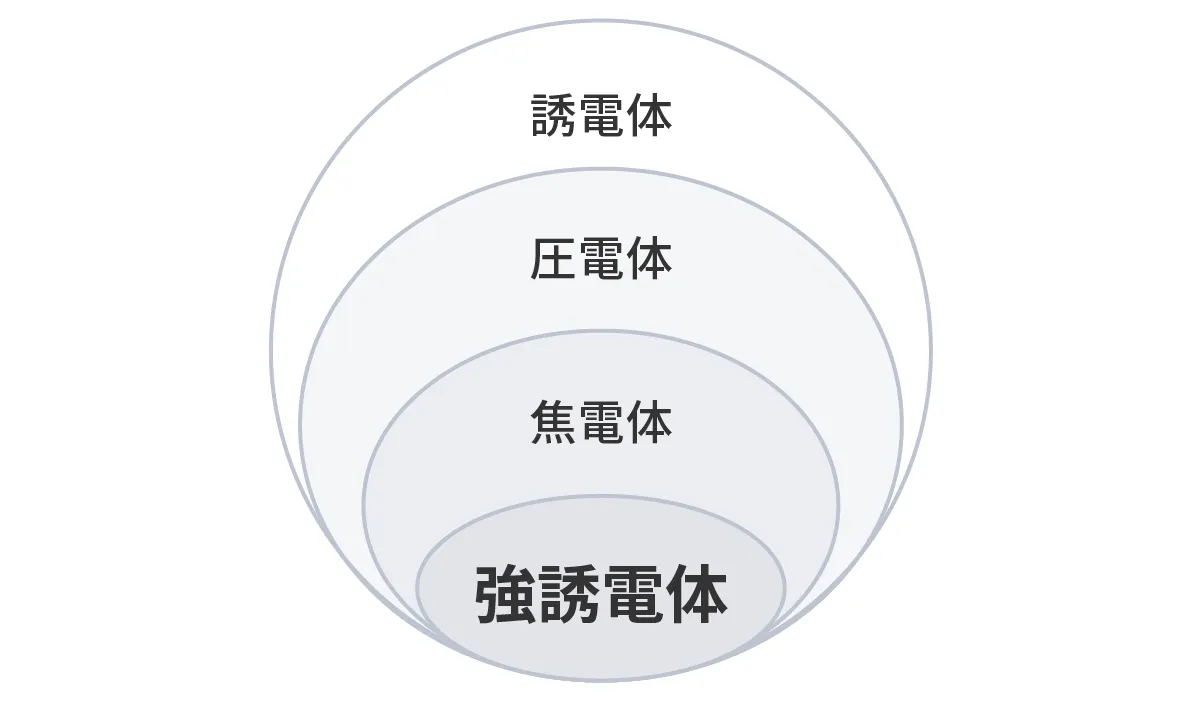

FeRAMは強誘電体材料としてPZT(チタン酸ジルコン酸鉛)を使用しています。PZTの結晶構造を図1に示します。PZT結晶の特性として、電圧を印加すると分極が発生し(Zr/Ti原子が結晶内部で上下し)、電圧の印加を止めても分極が残ることが分かっています。そのため、電界の向きにより原子には2つの安定点があり、これを不揮発性メモリの記憶素子として「0」「1」データに用いることを原理としています。

図1. PZT(チタン酸ジルコン酸鉛)の結晶構造

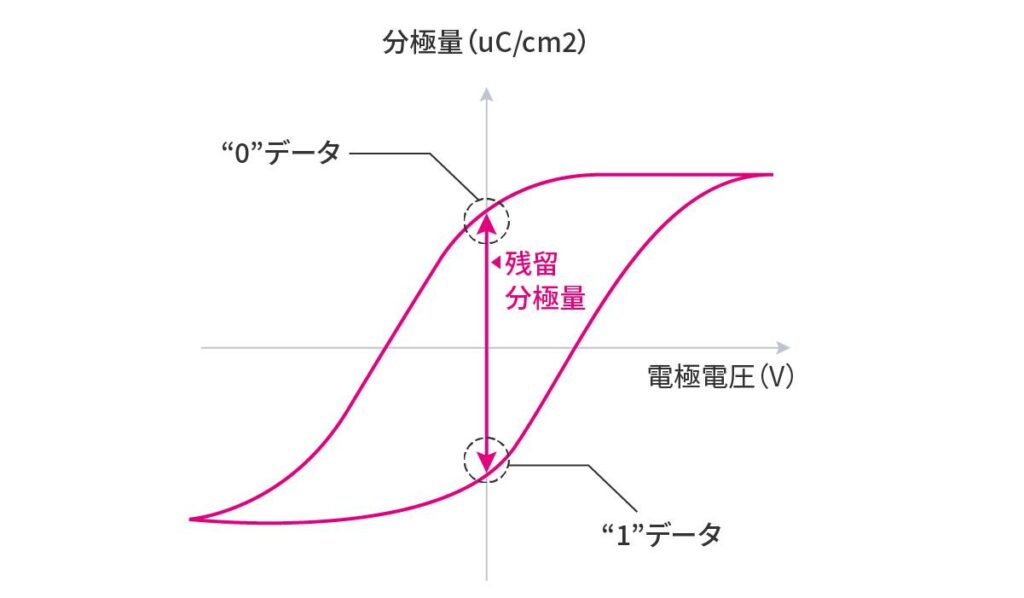

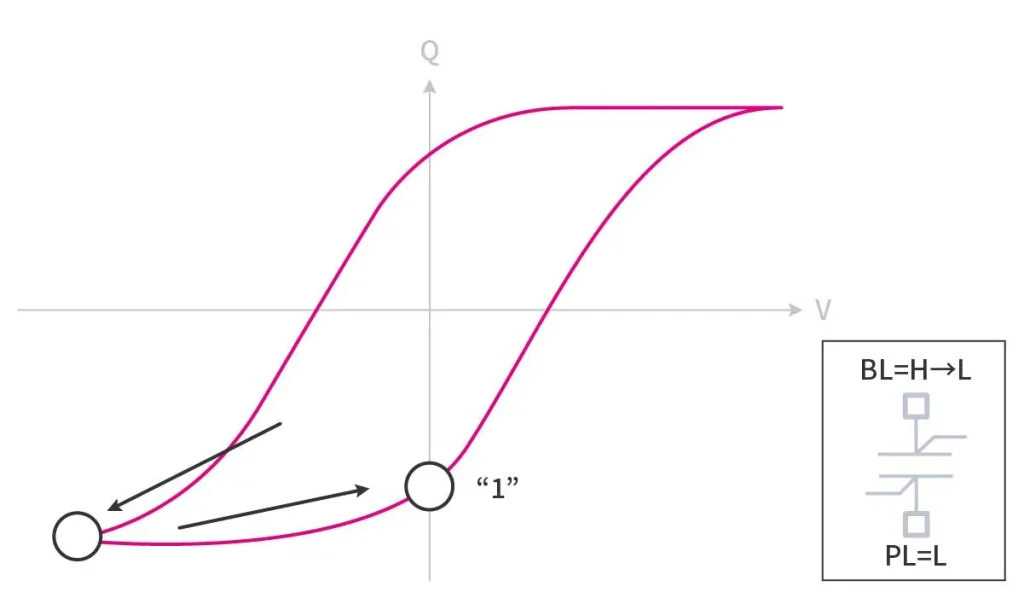

PZT結晶の分極量の電圧特性を図2に示します。分極量はヒステリシス特性を示し、電圧0V時の2つの安定点を「0」「1」データとして用います。Zr/Ti原子が結晶内部で上下する移動は物理的なダメージが少ないため、高書換え耐性の記憶素子となります。また、書換え時は、それ以前の安定点(「0」「1」データ)の状態によらず、電界の向きを変えるだけで次の安定点(「0」「1」データ)に遷移するため、特性比較表では「重ね書き」と表現しています。

図2. PZT結晶の分極量の電圧特性(ヒステリシス特性)

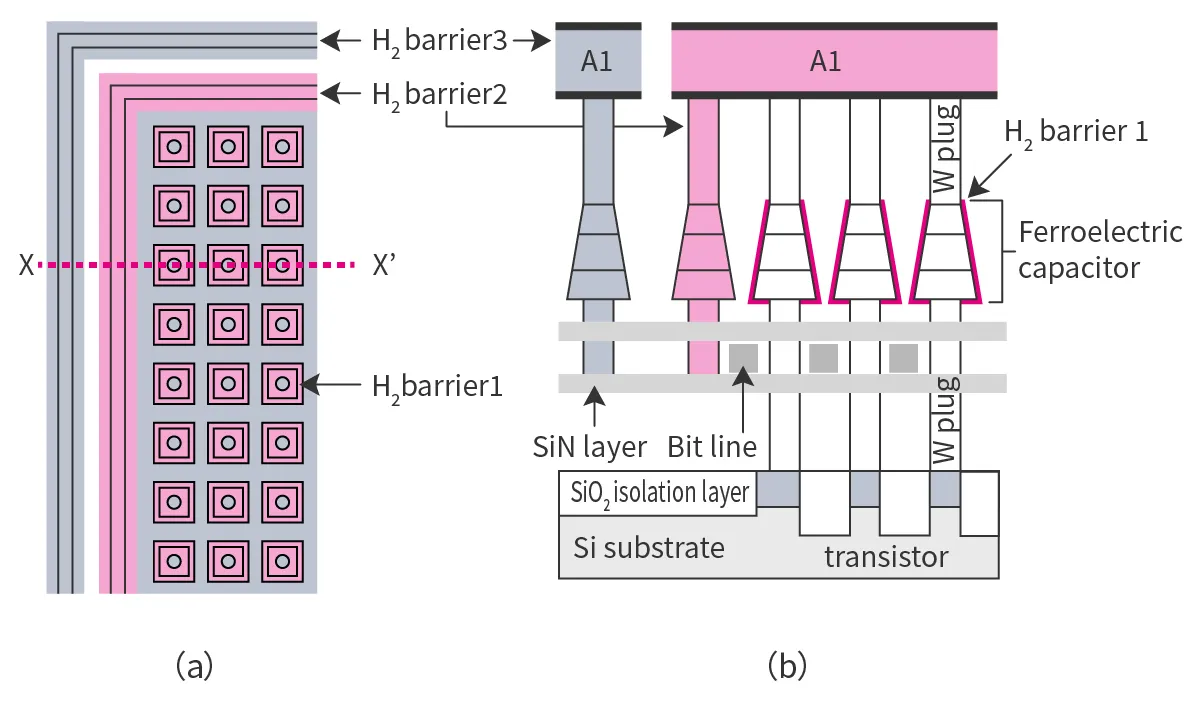

FeRAMのメモリセル構造

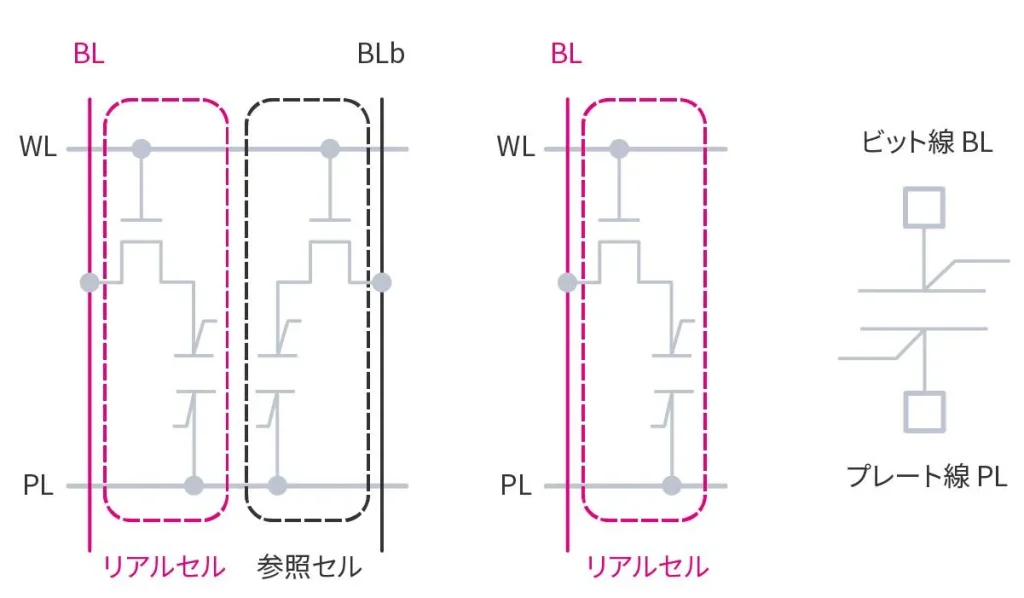

FeRAMのメモリセル構造は、1セルを2トランジスタ・2強誘電体キャパシタで構成する2T2C型(図3)、1セルを1トランジスタ・1強誘電体キャパシタで構成する1T1C型(図4)があります。強誘電体キャパシタは強誘電体材料を導電体(上部電極・下部電極)で挟み込んだキャパシタを指し、各導電体はビット線(BL)、プレート線(PL)に接続されます(図5)。

図3. 2T2C型メモリセル構造 図4. 1T1C型メモリセル構造 図5. 強誘電体キャパシタ

2T2C型は、リアルセルと参照セルを隣接配置し、参照セルはリアルセルと逆のデータを保持するよう回路動作します。リアルセルから出力されるビット線電圧(BL)と参照セルから出力されるビット線電圧(BLb)を比較して、BL>BLbの場合は「1」データ、BL<BLbの場合は「0」データと判別します。2つの強誘電体キャパシタを相補に用い、データ保持が安定するため、車載向けのような高信頼性用途の製品に適用しています。

1T1C型は、別回路で生成した参照電圧とリアルセルから出力されるビット線電圧(BL)を比較して、参照電圧>BLの場合は「1」データ、参照電圧<BLの場合は「0」データと判別します。1セルのメモリセル領域の面積が2T2C型の半分となるため、大容量製品に適用しています。

FeRAMの基本動作

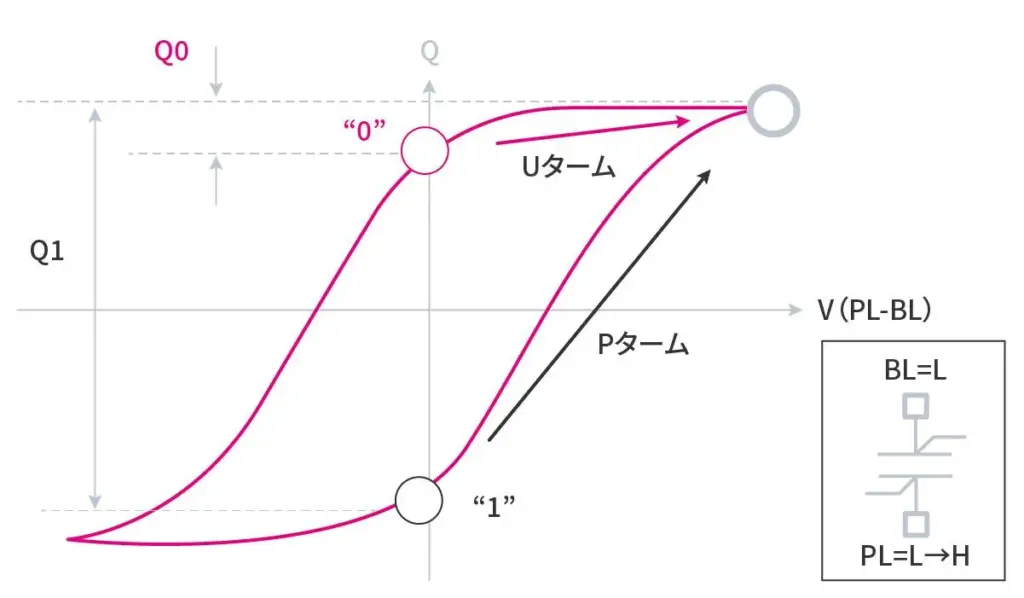

メモリセルの読み出し(Read)動作について図6に示します。強誘電体キャパシタのビット線(BL)に繋がる電極をLow、プレート線(PL)に繋がる電極をLowからHighへ電圧を印加(BL=L、PL=L→H)することで、読み出し動作します。PL=L→H時、強誘電体に保持されていた電荷が出力される際、安定点(「0」「1」データ)によって出力される電荷量Qが異なります。この電荷量の差を検出し、「0」「1」データを判断しますが、回路動作上はビット線に電位差として現れ、これをセンスアンプ活性で増幅し、データとして出力します。

図6. メモリセルの読み出し動作(ヒステリシス特性の遷移)

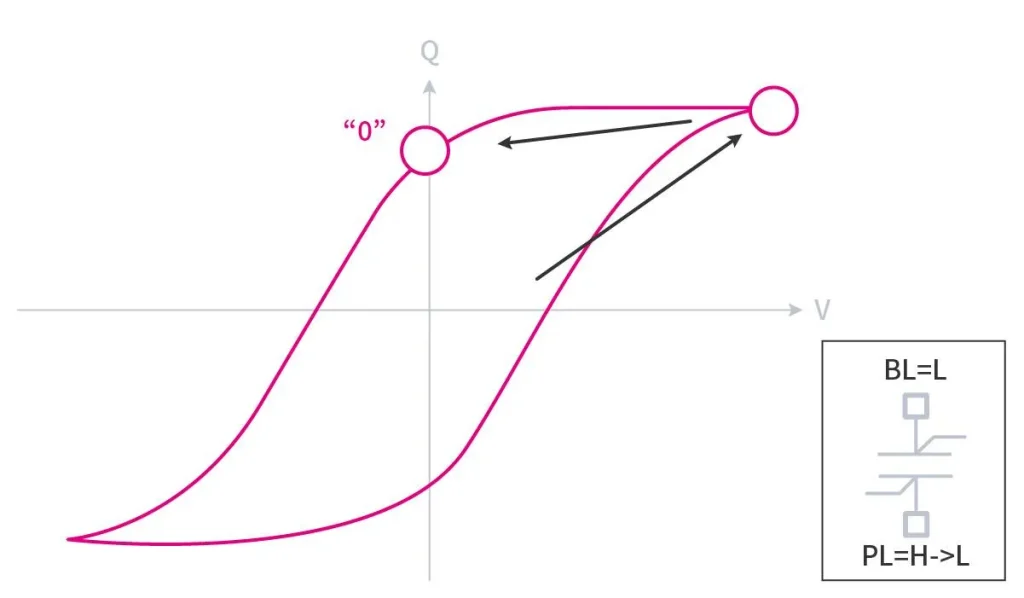

メモリセルの書き込み(Write)動作について図7、図8に示します。「0」データを書き込む場合、強誘電体キャパシタのビット線(BL)に繋がる電極をLow、プレート線(PL)に繋がる電極をHighに電圧印加(BL=L、PL=H)することで、書き込み動作します。その後、プレート線(PL)をLowにし、スタンバイ状態とし、「0」データで保持します。また、「1」データを書き込む場合、強誘電体キャパシタのビット線(BL)に繋がる電極をHigh、プレート線(PL)に繋がる電極をLowに電圧印加(BL=H、PL=L)することで、書き込み動作します。その後、ビット線(BL)をLowにし、スタンバイ状態とし、「1」データで保持します。

図7. メモリセルの書込み動作(ヒステリシス特性の遷移):「0」データの場合

図8. メモリセルの書込み動作(ヒステリシス特性の遷移):「1」データの場合