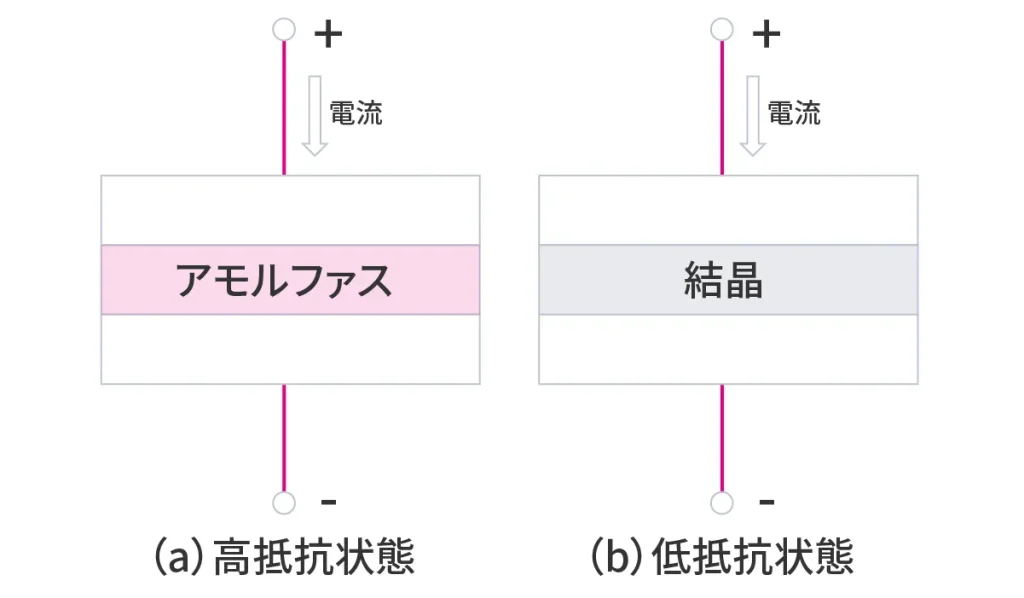

不揮発性メモリの仕組みについて — メモリの種類ごとに紹介

不揮発性メモリは電源がオフでもデータが消えないメモリの一種です。不揮発性メモリには様々な種類がありますが、電源がオフでもデータが消えない仕組みはメモリの種類によって異なっています。ここでは、それぞれの不揮発性メモリの仕組みについて解説します。

このページではFeRAM以外の不揮発性メモリの仕組みを紹介します。

FeRAMの仕組みについては以下のページを参照して下さい。

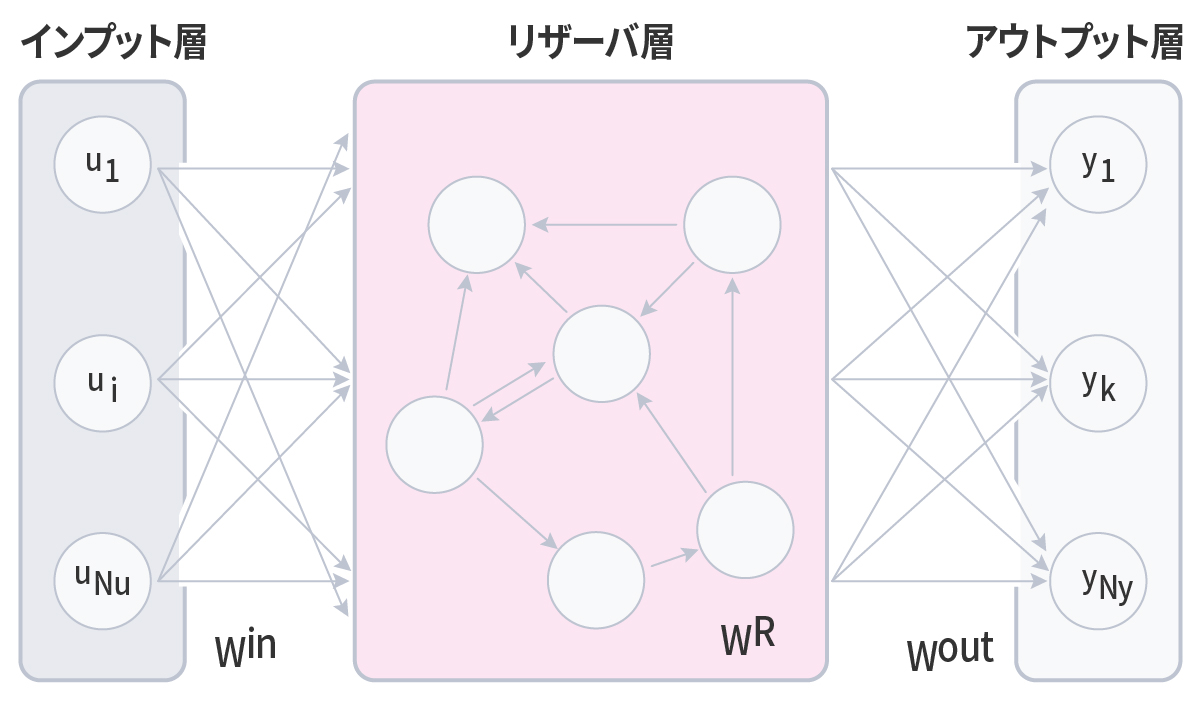

ReRAMの仕組み

2つの電極の間に置かれた金属酸化物などの絶縁体(タンタル、ハフニウムなどの金属酸化物がよく使われる)の抵抗の変化を利用して情報を記憶します(図1) [2] 。

2つの電極間に電圧をかけていくと、高抵抗状態(HR)にある絶縁体は、ある電圧で”フィラメント”とよばれる電流が流れる路ができ、低抵抗状態(LR)になります。

さらに電圧を高くすると、このフィラメントが消滅してLRにあった絶縁体はもとのHRとなります(過剰電流を流したフィラメントが熱により溶けて、電流を通さなくなることに似ています)。

元のHR状態にする場合、電極の極性を逆にして、フィラメントの酸化・還元反応を利用して書き換える場合が現在主流になっています。

情報を読み出す時は、情報を書き込む電圧より低い電圧を両電極にかけて、その電流を読み取ります。

高電圧をかけて大きな電流を流さなければ、記憶を書き換えられないために、不揮発のメモリとなります。

このようなしくみで動作するReRAMの他に、電極と絶縁体の間のショットキー障壁の高さの変化や酸化還元を利用して、HRとLRを作り出し、動作しているReRAMもあります。

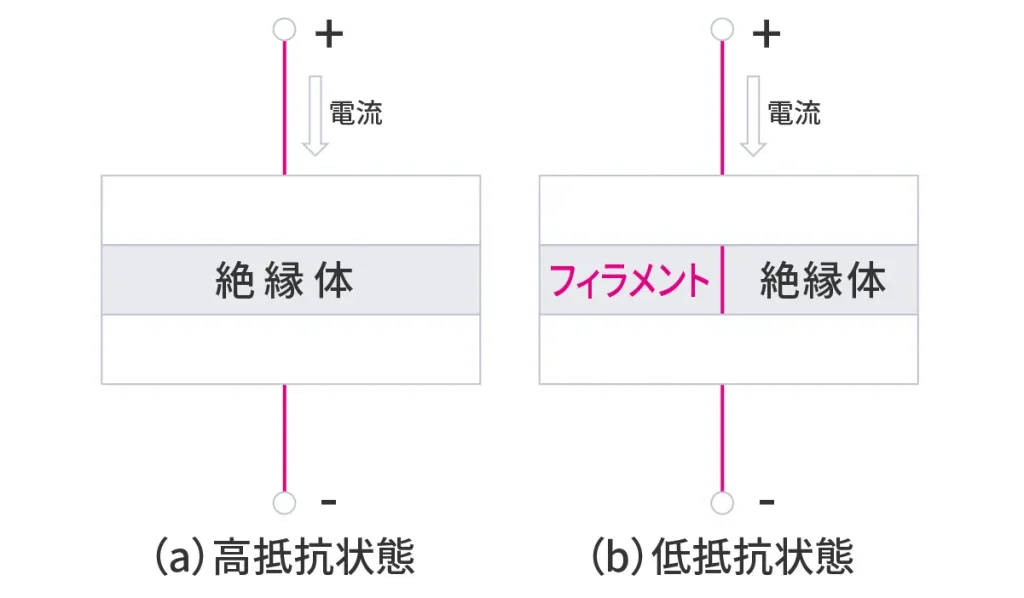

PCRAMの仕組み

2つの電極の間に置かれたカルコゲナイドとよばれる絶縁体(Ge2Sb2Te5がよく用いられます)などの抵抗の変化を利用して情報を記憶します(図2)[3]。

このような絶縁体は、アモルファス状態(ガラスのように構成する元素が無秩序に並んだ状態)のときは高抵抗状態(HR)で、結晶状態のときは低抵抗状態(LR)となります。

カルコゲナイドを挟んだ電極間に電圧をかけて電流を流すことにより、カルコゲナイドは熱せられ、ゆっくり電流を切れば結晶状態に、急に電流を切って急冷すればアモルファス状態にすることができ、情報の書き込みができます。

情報を読み出す時は、情報を書き込む電圧より低い電圧を両電極にかけて、その電流を読み取ります。温度を上げるような電流を流さなければ、記憶は不揮発に残ります。

PRAMでは、カルコゲナイドの他に、薄いGeTe層とSb2Te3層を何層にも繰り返して積層した(超格子構造)物質も使われることがあります。

PRAMでは、熱を利用することから、消費電力が高くなることや高密度に実装すると隣接する記憶単位同士が熱の影響でエラーが発生するなどの課題があります。

MRAMの仕組み

薄い絶縁体(MgOがよく使われる)を2つの磁石で挟んだ構造では、絶縁体を通して、2つの磁石に間に流れる電流(トンネル電流)は、その磁石の相対的な磁化方向によって変化します(トンネル磁気抵抗効果)。

MRAMは、この性質を利用した不揮発性メモリです(図3)[4]。

2つの磁石の磁化が同じ方向(平行状態)では、大きな電流を流すことができ(低抵抗状態:LR)、互いに反対(反平行状態)では、小さな電流しか流れません(高抵抗状態:HR)。

記憶の書き込みは、一方の磁石の磁化方向を変えて行います。

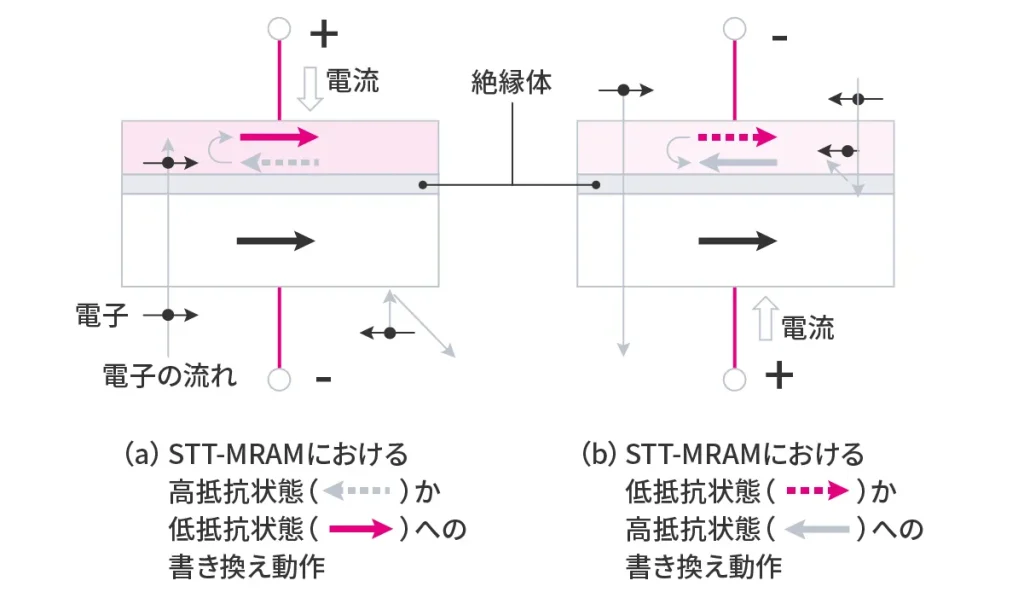

これには、主に2つの方式があり、1つは近接する配線に電流を流して発生する磁界を利用するトグル方式(トグルMRAMまたは単にMRAM)、もう一つは、2つの磁石間に流れる電流を利用するスピントランスファートルク方式(STT-MRAM)です。

後者では、電子が帯びる磁性(スピン)の磁化方向が、通過する磁石と同じ方向の場合に通過しやすい性質を利用します。

電子を下側から注入した場合(左図)、スピンが磁石と同じ方向の電子のみが絶縁体を通過し、反対側の磁石の磁化方向をスピンと同じ方向に反転させます(スピントランスファートルク)。

逆に上から電子を注入し(右図)、下の磁石を通過できなかった電子のスピンが上の磁石の磁化方向を反転させて、情報を書き換えます。

情報を読み出す時は、情報を書き込む電圧より低い電圧を両電極にかけて、その電流を測定します。情報を書き換えるような操作を行わない限り、記憶は不揮発にのこります。

一般にMRAMは、外部の磁界によって、保持している情報が書き換えられたしまうことや、トルク型MRAMでは磁石の反転に大きな電流が必要で、消費電力が大きくなること、STT-MRAMでは、電子のスピンが磁石の磁化方向を反転させるときに、ある確率で熱の影響により反転させられないことがあり、情報の書き換え時に工夫が必要になるなどの課題があります。

フラッシュメモリ、EEPROMの仕組み

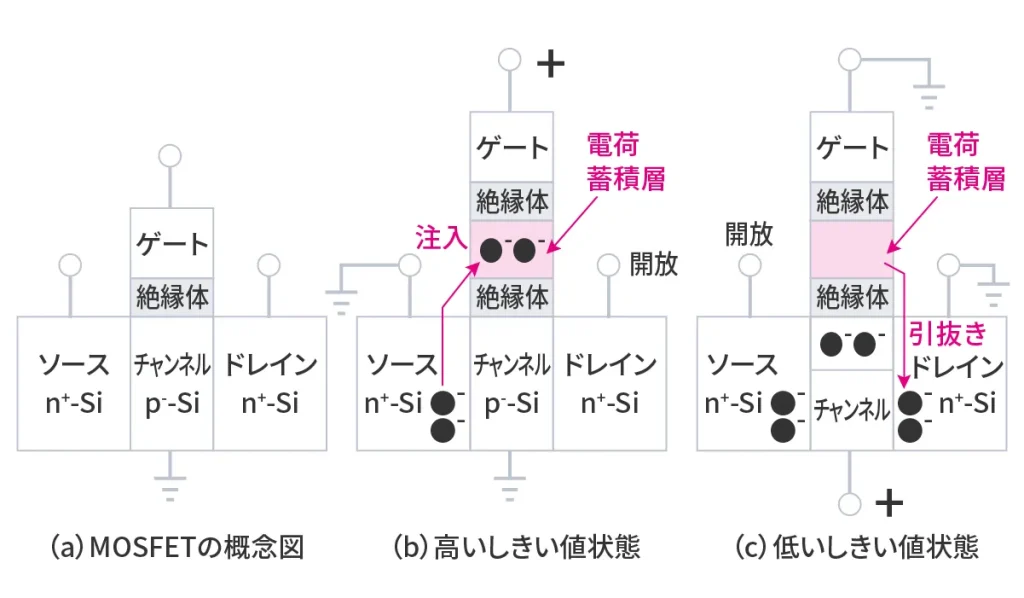

図4 MOSFET、FLASHメモリ、EEPROMの概念図

金属酸化膜半導体電界効果トランジスタ(MOSFET)のゲート部分に電荷を蓄積させることで、情報を不揮発に記憶する機能をもたせたメモリです。

現在半導体トランジスタが主流である、MOSFET(図7(a))は、ゲート部分に電圧を印加してチャネルと呼ばれる部分の抵抗を制御し、ソース、ドレイン間に流れる電流を制御することで、トランジターとして機能します。

ゲートへ正の電圧をかけていくとソース・ドレイン間に電流が流れ出すタイプのMOSFETを想定します。ソース、ドレイン間に電流が流れ出すときのゲートの電圧を「しきい値電圧」といいます。

図4 (b)と(c)はFLASHメモリ、EEPROMの記憶素子の例です。

ゲート電極(制御ゲート)下に絶縁膜を介して、電荷を蓄積する層(電荷蓄積層)を配置しています。電荷蓄積層に電子が蓄積された状態(図4(b))では、MOSFETのしきい値電圧が高くなり、高いゲート電圧をかけないとソース・ドレイン間に電流がながれません。

電荷蓄積層に電子がない状態(図4 (c))では、しきい値電圧が低くなり、低いゲート電圧でもソース・ドレイン間に電流がながれます。

フラッシュメモリ、EEPROMは、このしきい値電圧の違いで、情報を記憶します。

制御ゲートとソース間またはドレイン間に高電圧をかけて、絶縁膜を通して電子を蓄積または引き抜くことで、情報を書き換えます。

高電圧をかけて、電荷蓄積層への電子の蓄積、引き抜きを行わないかぎり、記憶は不揮発に残ります。

情報を読み出しは、制御ゲートに電圧をかけ、ソース・ドレイン間に流れる電流を測定し、しきい値電圧が高い状態あるか、低い状態にあるかを検出して行います。

EEPROMはこのような素子と通常のMOSFETを接続して一つのメモリ単位として構成しています。

フラッシュメモリでは、記憶部分の素子のみをいくつか直列に接続して、接続した記憶素子の記憶をグルーブ毎に書き込みまたは消去する方法を採用し、高集積化を実現しています。

以前は、高抵抗と低抵抗の2つの値を記憶するタイプが主流でしたが、現在は、電荷蓄積層への電子の蓄積量を何段階にも調整することで、一つの記憶素子で複数の記憶を保持できるようになりました。

さらに、以前Siウェーハ平面上につくられていた記憶素子を、立体的に配置することで、さらに高い記憶容量を実現しています。

平面的に配した記憶素子の場合、電荷蓄積層は、導電性の材料(フローティングゲート方式)が主流でしたが、立体的に配する記憶素子の場合は、絶縁膜が多く使われています。[1,5]

フラッシュメモリもEEPROMも情報の書き換え時に、電子が絶縁膜を通過することで、絶縁膜の絶縁耐性が劣化するために、書き換え回数は10万回ぐらいであること、書き換えを高電圧で行うために昇圧回路を設けなればいけないこと、このために消費電力が大きくなるなどの課題があります。

参考文献

[1] C. Zhao, et al., Materials 7, pp. 5117-5145 (2014).

[2] Y. Chen, IEEE T. Electron Dev. 67, pp. 420 – 433 (2020).

[3] M. L. Gallo and A. Sebastian J. Phys. D53, p. 213002 (2020).

[4] S. Ikegawa et al., IEEE T. Electron Dev. 67, pp.1407-1419 (2020)

[5] A. Goda, Electronics 10, p.3156 (2021).